(作者:是德科技产品经理 Shawn Lee) 键合线广泛应用于电子设备、半导体产业和微电子领域。它能够将集成电路(IC)中的裸片与其他电子元器件(如晶体管和电阻器)进行连接。键合线可在芯片的键合焊盘与封装基板或另一块芯片的相应焊盘之间建立电气连接。 半导体和电子设备制造市场正在持续扩展其版图。据《财富商业洞察》最近发布的一份报告中预测,到 2032 年,半导体市场预计将突破 20625.9 亿美元大关。随着市场需求的不断攀升,键合线测试的重要性亦随之日益凸显。这些连接对于将半导体裸片与封装引线或基板相连而言起着至关重要的作用。一旦这些键合工艺中出现任何缺陷,都可能引发诸如开路或短路等问题,进而对设备的整体性能造成严重影响。因此,进行键合线测试,不仅是为了确保产品的可靠性和降低生产成本,更是为了确保产品能够符合行业标准。 以下是影响键合线效果的一些常见缺陷: · 导线下垂:当导线受到张力时发生拉伸或下垂,就会导致接触不良,进而影响电气性能。 · 导线偏移:这是指在键合过程中导线发生横向移动,从而导致错位,进而造成连接不可靠。 · 形成引线环:若导线出现意外多余的部分,就可能会形成环状,这不仅会损害键合的质量,还会对设备的功能造成不利影响。 · 导线短路:这是一种极为严重的缺陷,具体表现为两根导线之间发生了意外的电气接触,进而可能引发电路故障,甚至导致整个设备的完全失效。 · 导线开路:这是指本应与焊盘形成电气连接的导线发生了断开,从而使得电路无法形成闭合回路,进而对设备的正常功能造成影响。 测试方法概述 测试键合线缺陷时,最广泛采用的方法包括使用自动 X 射线检测技术 (AXI) 进行光学/X 射线检测,以及借助自动测试设备 (ATE) 进行电气测试。 AXI 技术通过使用 X 射线的穿透能力,能够捕捉到键合线的精细图像,从而有效检测出如异物、空隙和密封不良等隐蔽缺陷。该方法属于非破坏性检测,非常适合检测复杂的组件。不过,其检测过程相对缓慢、成本也较高,而且存在辐射安全隐患。 另一方面,ATE通过对键合线的电气特性进行测试,能够准确识别出诸如开路、短路以及性能衰退等问题。该方法具有速度快、一致性强以及可编程等优点,是在大批量生产环境中应用的理想选择,但其可能无法有效检测出结构和机械方面的缺陷。 除了电气测试和光学检测手段外,还有其他多种技术可用于评估键合线的质量。例如,引线和键合的拉力测试可以测量键合线或带状键合的抗拉强度,球剪切测试可用于分析球键合的强度,热循环测试通过使键合线经历不同的温度条件来评估其耐久性;而应力测试旨在评估键合线在长时间内承受热应力和机械应力的能力。 电容测试作为一种新兴的检测手段,巧妙地利用了金属表面(例如键合线与金属板,后者亦称IC上方的传感板)的耦合特性。在此配置下,IC的每一个引脚和键合线都被有效地转换为电容器的导电板。这一方法使得用户可以检测到以往采用传统 ATE 和 X 射线方法难以发现的缺陷,比如键合线和内引线之间的 “近短路”现象,以及导线的垂直下垂问题。此外,电容测试还能识别出错误的芯片和模塑化合物等潜在问题。 电容测试原理 采用电容耦合法检测键合线缺陷的原理相对简单。具体而言,这一方法是通过共享电场,而非直接的电气连接,来在两个导体之间传递电能。如此,即便组件之间没有通过导线实现物理连接,也能进行信息通信或信号传输。 这一概念可应用于键合线的测试中,具体方法是测量两个导电物体表面之间的电容:一是键合线区域上方的电容结构,二是与键合线相关联的导电路径。通过对这两个导电物体表面所产生的电容响应进行分析,就可以评估封装集成电路内部键合线的状况及其位置情况。 如图 1 所示,非矢量测试增强探头 (VTEP) 就是实现此类测试的一个实例。该探头采用先进的电容和电感传感技术,旨在检测和测量印刷电路板(PCB)上各个元器件以及板内互连的电气特性。与传统测试方法相比,此项技术无需依赖详细的输入输出矢量即可进行操作,并具有出色的信噪比。

图 1:是德科技非矢量测试增强探头 (VTEP) 如下图 2 所示,该解决方案采用了先进的电容和电感传感技术,旨在检测和测量键合线的电容值。具体操作流程为:通过保护引脚,将刺激信号注入到引线框架中,随后该信号将会传输到键合线位置。当放大器触及传感器板(在本例中为电容结构)时,电路即刻闭合,并开始捕捉耦合响应。

图 2:使用 VTEP 的四方扁平封装 (QFP) 键合线测试装置的横截面图 通过采用这种方法,电气结构测试仪 (EST) 能够结合先进的电容和电感传感技术,以及零件平均测试 (PAT) 统计算法,从一系列已知完好的单元中学习并建立基线键合线测试。这样,用户就能准确的识别出任何偏离正常值的键合线变化,例如下图 3 中测试仪所捕捉到的“近似短路”缺陷。

图 3:使用 s8050 EST 检测到的 "近似短路"缺陷,并在 X 射线下进行验证 基于电容测试的优势和局限性 电容测试方法在处理周边引线排列的封装时尤为高效,原因在于这些引线均位于集成电路的同一侧或周围,彼此紧密相邻。典型的例子包括双列直插式封装(DIP)和四方扁平封装(QFP)。在这两类封装中,所有引线要么彼此相邻,要么环绕集成电路封装的周边。得益于此种设计,键合线得以通过单层结构围绕芯片布局,而不是相互堆叠。这种配置使得测量电容耦合信号以确定键合线的物理位置变得相对容易和精确。 然而,随着技术的不断进步以及集成电路复杂性的日益提升,一系列更先进的封装类型应运而生,其中包括球栅阵列 (BGA),此类封装涉及多层键合线的堆叠。如下图 4 所示,由于键合线排列的复杂性显著增加,所以这种先进的方法为测量电容耦合信号带来了更多的挑战。

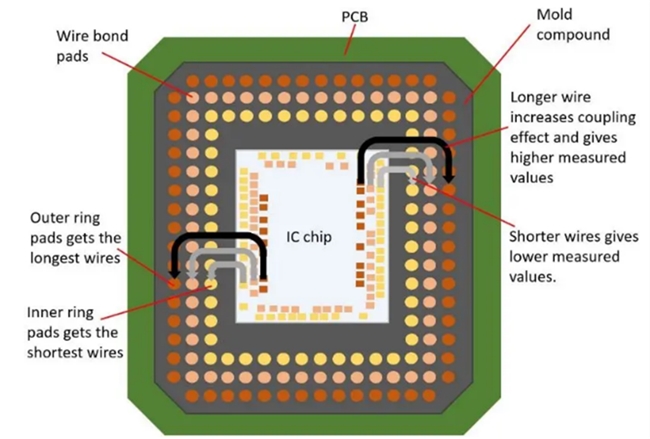

图 4:球栅阵列 (BGA) 封装俯视图 电容耦合方法可能并不适用于这些先进的集成电路封装类型。以BGA为例,其键合线焊盘是按照同心环的方式,即围绕芯片也围绕印刷电路板进行布局,由此产生了多层线路的堆叠。如图 5 所示,这种配置会影响电容耦合信号的强度和信噪比,进而使得测量电容耦合信号更具挑战性。

图 5:多条导线相互堆叠的 BGA 封装横截面图 因此,在选择电容耦合测试方法之前,对键合线排列方式的考量显得尤为重要。对于具有复杂键合线排列的先进封装类型,可能需要采用其他测试方法,进而确保测量的准确性以及缺陷检测的可靠性。 革新键合线缺陷检测技术,助推微电子行业前行 键合线技术在微电子领域中占据着举足轻重的地位,而随着市场增长预测的急剧上升,对于高效测试方法的需求也愈发迫切。尽管传统的 AXI 和 ATE 系统能提供有价值的分析见解,但它们也有很大的局限性。在集成电路中,会出现不同类型的键合线变形缺陷,而针对这些缺陷,也有各种对应的系统去进行处理。 ATE 系统可轻松检测诸如开路、短路和缺线等电气缺陷。这使得它们成为在高产量生产环境中的理想选择。然而,这些系统的局限性在于,它们只能检测电气缺陷,而对于其他类型的问题,比如多余或杂散的导线、近似短路的下垂导线或摆动线等,却无能为力。因此,有可能出现这样的情况:在 ATE 测试中,集成电路看似完全正常工作,但实际上却并非如此。 相比之下,AXI 可以检测出所有键合线缺陷。然而,这种方法需要人工目视检查,不仅费时耗力,而且容易受到人为因素的影响而导致误差。特别是在高产量生产环境下,想要对每一批集成电路封装进行细致的筛查显得尤为不切实际,因为这会大幅拖慢生产节奏,造成瓶颈。因此,在实际操作中往往只能随机选取少量样品进行筛选,这无疑限制了 AXI 在全面缺陷检测方面的效能。 基于电容的测试技术成功应对了这两项挑战。这一先进技术能够检测到那些传统 ATE 和 X 射线系统难以察觉的缺陷,例如键合线和内部引线之间的 “近似短路 ”以及垂直方向上的导线下垂问题。此外,它还能识别出芯片错误和模塑化合物问题等其他方面的异常,进而显著提升了其诊断能力。 与 PAT 统计分析相结合时,这种检测方式可以高效且轻松地检测出电气和非电气缺陷,并能适应快速的生产节奏。 关于是德科技 是德科技(NYSE:KEYS)启迪并赋能创新者,助力他们将改变世界的技术带入生活。作为一家标准普尔 500 指数公司,我们提供先进的设计、仿真和测试解决方案,旨在帮助工程师在整个产品生命周期中更快地完成开发和部署,同时控制好风险。我们的客户遍及全球通信、工业自动化、航空航天与国防、汽车、半导体和通用电子等市场。我们与客户携手,加速创新,创造一个安全互联的世界。了解更多信息,请访问是德科技官网。 |

- 河南仙门山仰韶部落大学入学测试,引爆国庆假期(2024-10-08)

- 旧路面废渣利用 赋能美绿高速(2024-09-30)

- 共探电池未来,铸就高效商贸社交,11月相聚上海振威电池工业展/超级(2024-09-23)

- 天玑科技参与编制的《信息技术应用创新 超融合系统测试规范》团体标(2024-07-25)

- 内蒙古福羲堂生物科技有限公司:利用地域优势打造健康绿色将康食品(2024-07-18)

- 济南高新区:“建设发展计划”、“土地开发利用三年计划”助力“三次(2024-05-21)